# RS45C Version 01J Security Target -Public Version-

**Renesas Electronics Corp.**

Kenji Hirao

# 0. History

# 0.1 Approval

| Name           |                   | Date            |

|----------------|-------------------|-----------------|

| Prepared       | Kenji Hirao       | 1 October, 2012 |

| Approved (1) — |                   | _               |

| Approved (2)   | Takashi Tsukamoto | 1 October, 2012 |

## 0.2 Revision

| Section      | Description                                              | Name              | Date             |

|--------------|----------------------------------------------------------|-------------------|------------------|

| _            | Release                                                  | Akira Yamanashi   | 07 March, 2008   |

| 0.3          | Remove "DPA" from the table                              | Akira Yamanashi   | 24 April, 2008   |

| 3.2.1.1      | Remove "DPA" described as example                        |                   |                  |

| 3.4.2        | Remove "DPA" described as example                        |                   |                  |

| 7.1          | Change the referece from [PM] to [SM]                    |                   |                  |

| 8.1          | Change the referece from [PM] to [SM]                    |                   |                  |

| 6.1.2.1      | Added the 3DES keying option 1 (168bit)                  | Akira Yamanashi   | 25 April, 2008   |

| 6.3.1        | Added the 3DES keying option 1 (168bit)                  |                   |                  |

| 7.1          | Added the 3DES keying option 1                           |                   |                  |

| 2.2.2        | Add FAU_SAS                                              | Akira Yamanashi   | 24 June, 2008    |

| 2.3          | Remove BSI-PP-0035                                       |                   |                  |

| 2.4.2, 2.4.3 | Change the descryption                                   |                   |                  |

| 6.1.1.1, 6.2 |                                                          |                   |                  |

| 5, 6.1.1.3   | Add the description                                      |                   |                  |

| 6.1, 6.1.3,  | Remove the descryption for MDIP                          |                   |                  |

| 6.3.1        |                                                          |                   |                  |

| 6.1.2.1      | Change the dependencies                                  |                   |                  |

| 7.3          | Remove this section                                      |                   |                  |

| 1.2          | Add package descryption                                  | Akira Yamanashi   | 30 July, 2008    |

| 1.2          | Deleted part of the figure with description              | Akiko Nobusawa    | 29 october 2008  |

| 1.2          | Deleted a description                                    |                   |                  |

| 2.2.3        | Deleted a bookmark for a section number and added "and"  |                   |                  |

| 2.4.2        | Added a phrase                                           |                   |                  |

| 4.1.3        | Deleted a description                                    |                   |                  |

| 4.2.1        | Refrased the security objectives and added a description |                   |                  |

| 6.1.1.1      | Deleted a few descriptions                               |                   |                  |

| 6.2.1        | Added descriptions                                       |                   |                  |

| 6.2.2        | Added descriptions                                       |                   |                  |

| 6.2.3        | Added descriptions                                       |                   |                  |

| 6.2.4        | Added descriptions                                       |                   |                  |

| 6.3          | Added descriptions in Table 6-4                          |                   |                  |

| 7.3          | Deleted a description                                    |                   |                  |

| 3.2.2        | Deleted description                                      | Yasuaki Nishimura | 13 February 2009 |

| 4.1.3        | Deleted description                                      |                   |                  |

| 6.2          | Modified description                                     |                   |                  |

| 6.2.1        | Added description                                        |                   |                  |

| 3.2.2        | Delete a description                                     | Yasuaki Nishimura | 10 March 2009    |

| 4.1.3        | Delete a description                                     |                   |                  |

| 1.2          | Added DES library for RS-4                               | Yasuaki Nishimura | 1 September 2009 |

RENESAS

| 1.4.1.2       | Modified DES coprocessor                                    |                          |                   |  |

|---------------|-------------------------------------------------------------|--------------------------|-------------------|--|

|               |                                                             | Modified DES coprocessor |                   |  |

| 4.1.2         | Added DES library for RS-4                                  |                          |                   |  |

|               | Deleted note                                                |                          |                   |  |

| 6.1           | Deleted Single DES                                          |                          |                   |  |

| 6.1.2.1       | Deleted Single DES                                          |                          |                   |  |

| 6.3.1         | Deleted Single DES                                          |                          |                   |  |

|               | De;eted Single DES in Table.6-4 and Table.6-6               |                          |                   |  |

| 7.1           | Deleted Single DES                                          |                          |                   |  |

|               | Added Application Notes for SF.DES                          |                          |                   |  |

| 7.2           | Deleted Single DES in Table.7-1 and Table.7-2               |                          |                   |  |

|               | Deleted Single DES                                          |                          |                   |  |

| 8.1           | Modified CC reference                                       |                          |                   |  |

| 0.3           | Mis description                                             | Yasuaki Nishimura        | 2 September 2009  |  |

| Abbreviations |                                                             |                          |                   |  |

| 1.4.1.1       | Mis description                                             |                          |                   |  |

| 8.1           | Mis description                                             |                          |                   |  |

| 3.2.2         | Deleted T.NoSWDetect                                        | Yasuaki Nishimura        | 8 September 2009  |  |

| 4.1.3         | Deleted O.SWDetect                                          |                          |                   |  |

| 4.3           | Deleted T.NoSWDetect in Table.4-1                           |                          |                   |  |

| 6.1           | Modified TOE deateures                                      |                          |                   |  |

| 6.3           | Deleted [DES] from Table.6-3                                | Yasuaki Nishimura        | 29 September 2009 |  |

| 1.1           | Modified Rev. No.                                           | Koji Oyabu               | 14 December, 2011 |  |

| 1.2           | Modified Version of DES library and UGM                     |                          |                   |  |

| 7.2           | Add FCS_RNG.1 in Table.7-1                                  |                          |                   |  |

| 7.3           | Add SF.HWprotect in Table.7-2                               |                          |                   |  |

| 7.3           | Modified FCS_RNG.1 description                              |                          |                   |  |

| 1.1, 1.2      | Modified TOE Version (01 to 01J)                            | Koji Oyabu               | 16 December, 2011 |  |

| 3.2.2         | Modified definition of threat                               | Naoki Ushimi             | 28 June, 2012     |  |

|               | Review the description about TOE Summary Specification      | Naoki Ushimi             | 28 June, 2012     |  |

|               | for evaluation body and certification body.                 |                          | ,                 |  |

|               | Term correction (failure condition to dangerous condition). | Kenji Hirao              | 11 July, 2012     |  |

|               | Separated description of SFR.                               | 5                        | •                 |  |

|               | Modified description that how the TOE summary               | Naoki Ushimi             | 22 August, 2012   |  |

|               | specification meets each SFR. These TOE summary             |                          | <i>U</i> ,        |  |

|               | specification are EWE Interrupt and RAM Mirroring           |                          |                   |  |

|               | Function.                                                   |                          |                   |  |

|               | ST-Lite created from ST(Rev.5588)                           | Kenji Hirao              | 1 October, 2012   |  |

| .2            |                                                             |                          | , *=              |  |

# **0.3 Abbreviations**

| Term   | Meaning                                                                                                   |  |

|--------|-----------------------------------------------------------------------------------------------------------|--|

| CBC    | Cipher Block Chaining                                                                                     |  |

|        | A mode of DES encryption.                                                                                 |  |

| CC     | Common Criteria (ISO 15408)                                                                               |  |

| СОТ    | Chip-on-Tape - an IC packaged in a form suitable for embedding into a plastic card to form a security IC. |  |

| CPU    | Central Processing Unit                                                                                   |  |

| CRAM   | RAM dedicated for use by MMC coprocessor                                                                  |  |

| CRC    | Cyclic Redundancy Check                                                                                   |  |

| DES    | Data Encryption Standard                                                                                  |  |

| DFA    | Differential Fault Analysis                                                                               |  |

| EAL    | Evaluation Assurance Level                                                                                |  |

| ECB    | Electronic Code Book                                                                                      |  |

|        | A mode of DES and 3DES encryption.                                                                        |  |

| EEPROM | Electronically Erasable Programmable Read-Only Memory                                                     |  |

| HW RNG | Hardware random number generator (physical random number generator)                                       |  |

| IC     | Integrated Circuit                                                                                        |  |

| ISC    | Integrated Security Concept                                                                               |  |

| IT     | Information Technology                                                                                    |  |

| MCU    | Micro Computer Unit                                                                                       |  |

| MMC    | Modular Multiplication Coprocessor                                                                        |  |

| PKI    | Public Key Infrastructure                                                                                 |  |

| PP     | Protection Profile                                                                                        |  |

| PRNG   | Pseudo Random Number Generator                                                                            |  |

| RAM    | Random Access Memory                                                                                      |  |

| RL     | Random Logic (Glue Logic)                                                                                 |  |

| RNG    | Random Number Generator                                                                                   |  |

| ROM    | Read-Only Memory                                                                                          |  |

| RSA    | Rivest, Shamir, Adelmann – a public key encryption algorithm, named after its inventors.                  |  |

| SFP    | Security Function Policy                                                                                  |  |

| SFR    | Security Functional Requirement                                                                           |  |

| ST     | Security Target                                                                                           |  |

| TOE    | Target of Evaluation                                                                                      |  |

| TSF    | TOE Security Functionality                                                                                |  |

| WAP    | Wireless Application Protocol                                                                             |  |

# 0.4 Glossary

| Term                  | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Embedded Software     | Software held in the chip, having been developed by users of the TOE. Such software generally includes an operating system and may include all or part of applications. There are two types of Embedded Software:<br>• Hard-coded – held in ROM                                                                                                                                                                                                            |  |

|                       | <ul> <li>Soft-coded – held in EEPROM or RAM.</li> <li>The chip does not depend on such software, and Embedded Software is not part of the TOE. However, hard-coded Embedded Software will be included in the ROM of any issued TOE at manufacturing time.</li> <li>Note that Embedded Software includes all software on a TOE other than the IC Dedicated Software.</li> </ul>                                                                             |  |

|                       | Embedded Software is also referred to as 'Security IC Software' (especially in [BSI-PP-0035]).                                                                                                                                                                                                                                                                                                                                                             |  |

| EWE                   | An interrupt generated by the TOE whenever an attempt is made to write to EEPROM. The interrupt results in a jump to the address held at a fixed location in the memory map allowing embedded software to be executed. The embedded software is not part of the TOE.                                                                                                                                                                                       |  |

| IC Dedicated Software | Software developed by Renesas and embedded in the IC. (Adopted from [BSI-PP-0035])                                                                                                                                                                                                                                                                                                                                                                         |  |

| IC Dedicated Test     | Software developed by Renesas for testing the TOE during manufacture. This software is                                                                                                                                                                                                                                                                                                                                                                     |  |

| Software              | part of the TOE, but is not available for general use by operating systems, applications or end-users in phase 7 of the lifecycle (see section 1.4.3).                                                                                                                                                                                                                                                                                                     |  |

| Manufacturing         | Some basic data injected into EEPROM, enabling traceability of an IC to the lot and line in                                                                                                                                                                                                                                                                                                                                                                |  |

| Identification Data   | which it was manufactured, the Security IC Embedded Software present, and the versions of masks and specifications applicable.                                                                                                                                                                                                                                                                                                                             |  |

| Option List           | <ul> <li>A form supplied by Renesas and filled in by a TOE customer, specifying various options for the manufacture of TOE ICs for that customer. The aspect of particular interest to this security target is :</li> <li>Selection of whether pre-personalisation data injection is required The option list also describes the content and structure of the manufacturing identification data that Renesas will inject (see section 1.4.4.2).</li> </ul> |  |

| Renesas               | Refer to Renesas Electronics Corp. (http://www.renesas.com/)                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Reset state           | A state in which the chip does not execute instructions or engage in input/output. The chip can exit the reset state by receiving an external reset.<br>See also section 7.1.                                                                                                                                                                                                                                                                              |  |

| Smartcard             | Composition of the TOE, the Smartcard Embedded Software, User Data and the package (the smartcard carrier).                                                                                                                                                                                                                                                                                                                                                |  |

| TOE                   | Target of Evaluation. TOE consists of the chip (IC) and other materials and data.<br>However, the term is sometimes used to indicate just the chip.                                                                                                                                                                                                                                                                                                        |  |

| TOE Delivery          | The point at which the TOE is delivered, as shown in section 1.4.3. This may be either in the form of wafers (at the end of phase 3) or as packaged modules (at the end of phase 4).                                                                                                                                                                                                                                                                       |  |

| TOE Manufacturer      | (As defined in section 8.7 of [BSI-PP-0035]) The IC developer and manufacturer. If the TOE is delivered after phase 4 (i.e. as packaged modules, rather than wafers) then this is also the packager.<br>For the RS45C, the TOE Manufacturer refers to Renesas.                                                                                                                                                                                             |  |

| TSF Data              | Data created by and for the TOE and that might affect the operation of the TOE.                                                                                                                                                                                                                                                                                                                                                                            |  |

| UART                  | Universal Asynchronous Receiver Transmitter – in accordance with ISO/IEC7816-3.                                                                                                                                                                                                                                                                                                                                                                            |  |

| User Data             | All data managed by the Security IC Embedded Software in the application context. User data comprises all data in the final Security IC except for the TSF data.                                                                                                                                                                                                                                                                                           |  |

| User Mode             | The mode of operation after TOE Delivery. The TOE is set to this mode just before delivery, which renders the IC Dedicated Test Software permanently unavailable.                                                                                                                                                                                                                                                                                          |  |

| WDT                   | Watchdog Timer – a feature of the chip that enables embedded software to be regularly executed during the operation of the IC. This allows checks to be made on the execution environment to help detect potential attacks or insecure conditions.                                                                                                                                                                                                         |  |

| 1. | ST Introduction                                                                                          |  |

|----|----------------------------------------------------------------------------------------------------------|--|

|    | 1.1 ST Reference                                                                                         |  |

|    | 1.2 TOE Reference                                                                                        |  |

|    | 1.3 TOE Overview                                                                                         |  |

|    | 1.4 TOE Description                                                                                      |  |

|    | 1.4.1 RS45C Product Description                                                                          |  |

|    | 1.4.2 TOE Intended Usage                                                                                 |  |

|    | 1.4.3 TOE Lifecycle                                                                                      |  |

|    | 1.4.4 TOE Environments                                                                                   |  |

| 2. | Conformance Claims                                                                                       |  |

|    | 2.1 CC Conformance Claim                                                                                 |  |

|    | 2.2 PP Claims                                                                                            |  |

|    | 2.2.1 PP Reference                                                                                       |  |

|    | 2.2.2 PP Tailoring                                                                                       |  |

|    | 2.2.3 PP Additions                                                                                       |  |

|    | 2.3 Package Claim.                                                                                       |  |

|    | 2.4 Conformance Rationale                                                                                |  |

|    | 2.4.1 CC Conformance Rationale                                                                           |  |

|    | 2.4.2 PP Claim Rationale                                                                                 |  |

|    | 2.4.3 Package Claims Rationale                                                                           |  |

| 3. | Security Problem Definition                                                                              |  |

| 5. | 3.1 Description of Assets                                                                                |  |

|    | 3.2 Threats                                                                                              |  |

|    | 3.2.1 Threats Defined in [BSI-PP-0035]                                                                   |  |

|    | 3.2.2 Other Threats                                                                                      |  |

|    | 3.3 Organisational Security Policies                                                                     |  |

|    | 0                                                                                                        |  |

|    | <ul><li>3.3.1 Policy Requirement from [BSI-PP-0035]</li><li>3.3.2 Policy Requirement from [PA]</li></ul> |  |

|    |                                                                                                          |  |

|    | 3.4 Assumptions<br>3.4.1 Assumptions from [BSI-PP-0035]                                                  |  |

|    | 1                                                                                                        |  |

|    | 3.4.2 Assumptions from [PA]                                                                              |  |

| 4  | 3.4.3 Other Assumptions                                                                                  |  |

| 4. | Security Objectives                                                                                      |  |

|    | 4.1 Security Objectives for the TOE                                                                      |  |

|    | 4.1.1 Objectives from [BSI-PP-0035]                                                                      |  |

|    | 4.1.2 Objectives Based on [PA]                                                                           |  |

|    | 4.1.3 Other Objectives                                                                                   |  |

|    | 4.2 Security Objectives for the Environment                                                              |  |

|    | 4.2.1 Security objectives for the security IC Embedded sof                                               |  |

|    | development environment from [BSI-PP-0035]                                                               |  |

|    | 4.2.2 Security Objectives for the Operational Environment                                                |  |

|    | [BSI-PP-0035]                                                                                            |  |

|    | 4.2.3 Other Environment Security Objectives                                                              |  |

| _  | 4.3 Security Objectives Rationale                                                                        |  |

| 5. | Extended Components Definition                                                                           |  |

|    | 5.1 Extended Components Definition from [BSI-PP-0035]                                                    |  |

|    | 5.1.1 Definition of the Family FCS_RNG                                                                   |  |

|    | 5.1.2 Definition of the Family FMT_LIM                                                                   |  |

|    | 5.1.3 Definition of the Family FAU_SAS                                                                   |  |

# Table of Contents

| 6. | Secur | rity R | equirements                                            |    |

|----|-------|--------|--------------------------------------------------------|----|

|    | 6.1   | Sec    | curity Functional Requirements                         |    |

|    | 6     | 5.1.1  | Security Functional Requirements from [BSI-PP-0035]    |    |

|    | 6     | 5.1.2  | Security Functional Requirements Based on [PA]         |    |

|    | 6.2   | Sec    | curity Assurance Requirements                          |    |

|    | 6     | 5.2.1  | Refinements of the TOE Security Assurance Requirements |    |

|    | 6     | 5.2.2  | Refinements regarding CM scope (ALC_CMS)               |    |

|    | 6     | 5.2.3  | Functional specification (ADV_FSP)                     |    |

|    | 6     | 5.2.4  | Rationale for the Assurance Requirements               |    |

|    |       |        | curity Requirement Rationale                           |    |

|    | 6     | 5.3.1  | Rational for the Security Functional Requirements      |    |

|    | 6     | 5.3.2  | Dependencies of Security Functional Requirements       |    |

| 7. | TOE   | Sum    | nary Specification                                     | 44 |

|    | 7.1   | TO     | E Security Functionalities                             | 44 |

| 8. |       |        | -                                                      |    |

|    | 8.1   | Ref    | ference Materials                                      |    |

|    | 8.2   | Oth    | iers                                                   |    |

|    |       |        |                                                        |    |

# List of Figures

| Figure 1-1: Configuration of the TOE                | 2  |

|-----------------------------------------------------|----|

| Figure 1-2: Internal Block Diagram of the TOE       | 4  |

| Figure 1-3: Design and Manufacturing Lifecycle      |    |

| Figure 6-1: Paradigm Regarding Operating Conditions | 32 |

## List of Tables

| Table 1-1: TOE Configuration                                                       | 1  |

|------------------------------------------------------------------------------------|----|

| Table 4-1: Coverage of Security Assumptions, Policies and Threats by Objectives    |    |

| Table 6-1: Assurance Components                                                    | 37 |

| Table 6-2: Security Assurance Requirements, overview of differences of refinements | 38 |

| Table 6-3: Security Requirements versus Security Objectives                        | 40 |

| Table 6-4: Completion of SFRs                                                      | 42 |

| Table 6-5: Dependencies of Security Functional Requirements                        | 42 |

| Table 6-6: Additional SFR Dependencies                                             | 43 |

|                                                                                    |    |

# 1. ST Introduction

The ST aims to provide potential users of the TOE with

- A definition of the main properties of the IC that are evaluated and certified independent of any software

- Confidence in IC properties that can be used to build an integrated TOE (i.e. IC + operating system + other application software).

## **1.1 ST Reference**

Title: RS45C Version 01J Security Target –Public Version-

Revision: \$Rev:: 5639 \$

Provided by: Renesas Electronics Corp.

This Security Target applies to the Renesas RS45C integrated circuit (version 01J) (as defined in detail in the configuration list for the evaluation).

## **1.2 TOE Reference**

The TOE configuration is summarised in the table below:

| Item Type | Item                                            | Version                                         | Form of delivery                                                                                  |

|-----------|-------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Hardware  | RS45C integrated circuit                        | 01J                                             | Wafer or packaged module (see section 1.4.3)                                                      |

| Software  | IC Dedicated Test Software<br>Test ROM software | 2080                                            | Included in RS45C test ROM                                                                        |

| Software  | RNG on-line test software                       | 1.40<br>(defined by<br>the version<br>of [UGM]) | Hardcopy: provided as a part of [UGM]. (This is implemented in the Embedded Software by the user) |

| Software  | DES library for RS-4                            |                                                 | Electronic data/                                                                                  |

|           | RS4_LL.lib                                      | 4658                                            | Hardcopy:provided as a part of                                                                    |

|           | RS4_LL.txt                                      | 4658                                            | [UGM]. (This is implemented in the                                                                |

|           | RS4_LL.h                                        | 4658                                            | Embedded Software by the user)                                                                    |

| Document  | Hardware Manual                                 | 1.00                                            | Electronic data/Hardcopy                                                                          |

| Document  | User Guidance                                   | 1.40                                            | Electronic data/Hardcopy                                                                          |

| Document  | Option List                                     | 1.1                                             | Electronic data/Hardcopy                                                                          |

Further description of the TOE is provided in section 1.4.1.

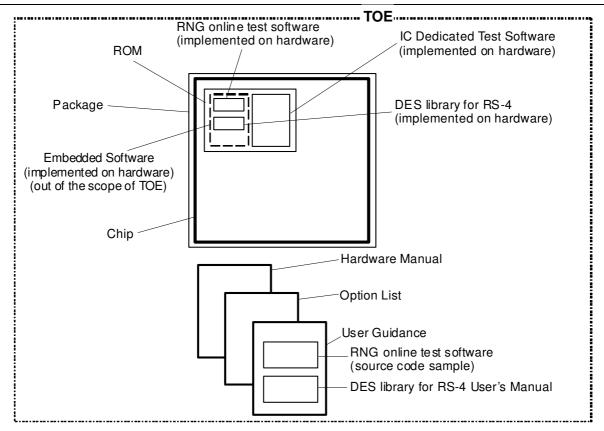

**Figure 1-1: Configuration of the TOE**

Figure 1-1 shows the configuration of the TOE. The TOE consists of hardware, software, and documents. The software (as part of the TOE) is provided as being implemented on the hardware. Among software, the Embedded Software is outside the scope of the TOE. The RNG online test software is provided to the developer of the Embedded Software as a source code sample in [UGM], and it is implemented in the TOE as the embedded software by the Embedded Software developer.

# **1.3 TOE Overview**

This document is the ST for the Renesas RS45C IC product, intended for use as a Security IC. The TOE complies with the Eurosmart Protection Profile developed by the Secure Semiconductor Vendor Group [BSI-PP-0035]. However, the TOE also provides a number of additional security features that have been based on a long history of assisting software developers to implement secure Security IC Embedded Software. These TOE-specific security features have been added to the ST.

The TOE is ideally suited for high security applications. Security has been built in from the start, forming an integral part of the whole Composite Product design concept. The whole development process (including secure chip design environment, secure production facilities and secure handling during shipment to the customer) is constantly reviewed in order to maximise the overall security package. The TOE can be delivered either in the form of wafers, or as packaged modules ready for embedding into a plastic card.

Many security features such as integrated sensors, distributed layout, random number generation, DES coprocessor and power analysis attack protection are all included providing a strong onchip hardware security structure. Uniquely, Renesas Security ICs are fabricated using a MONOS (Metal Oxide Nitride Oxide Silicon) EEPROM structure. MONOS advantages compared to standard EEPROM structures are high resistance to radiation disturbance, high reliability and endurance.

The TOE fulfils the requirements of security applications requiring large memory, high security and high speed secure authentication, data encryption or electronic signature. Examples include: PKI, WAP, e-m-commerce, digital signature, USIM/UMTS, and credit card.

Where public key is a core requirement, a high speed MMC able to process arithmetical data in a time frame that ensures a fast and free flowing application environment is required. The MMC ensures the high performance required by today's high security applications.

Applications such as WAP and e-m-commerce are ever expanding in scope and consequently the need for greater memory storage for both data and program code is ever increasing. The TOE provides a significant increase in ROM for program storage over previous devices whilst ensuring a balance of EEPROM for data storage.

## **1.4 TOE Description**

#### 1.4.1 RS45C Product Description

The TOE consists of the hardware shown in Figure 1-2, along with IC Dedicated Test Software, some embedded software, and reference and guidance documents. IC Dedicated Test Software is used in IC production only, and is not available to users.

As well as the functional interfaces, the IC surface is also considered as a TOE interface for some potential physical attacks, as described in section 3.2 of [BSI-PP-0035].

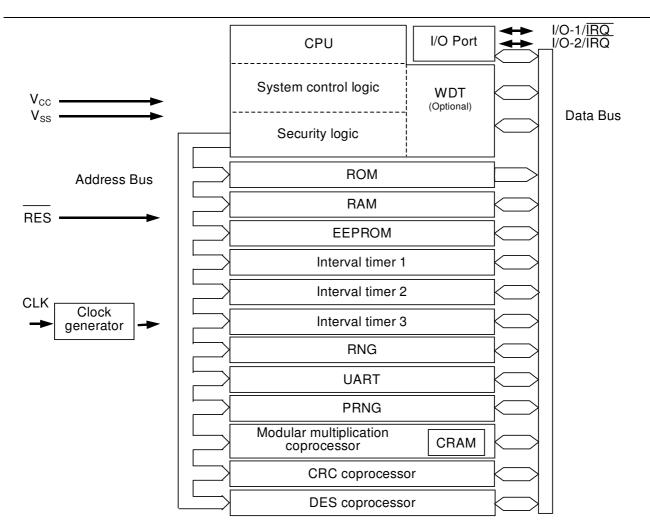

A block diagram of the chip is shown in Figure 1-2 below:

Figure 1-2: Internal Block Diagram of the TOE

### 1.4.1.1 Hardware

The TOE is an integrated circuit based around the high-speed RS-4 Series CPU core. As can be seen from the block diagram in Figure 1-2, the MCU comprises the following major blocks in addition to the CPU: ROM, RAM, EEPROM, random number generator (RNG), MMC, DES coprocessor, CRC coprocessor, UART, three interval timers, WDT (optional), and two I/O lines.

**CPU:** the CPU can operate with either a 3V or 5V supply and a maximum internal clock frequency is 20MHz:

- The instruction set is implemented with 16-bit variable instruction lengths (2 to 10 bytes) and permits register to register arithmetic and logic operations.

- A linear address space of up to 16 Mbytes is possible.

- Signed or unsigned multiply instruction (8 x 8, or 16 x 16-bits)

- Signed or unsigned divide instruction  $(16 \div 8, 16 \div 16, 32 \div 16$ -bits)

- Special EEPROM write instruction (EEPMOV.B and EEPMOV/P.W) and high-speed block transfer instruction (EEPMOV.W)

**Memory:** the TOE has a memory mapped architecture and allows the EEPROM to be used for both data and program storage. There is a special block of RAM dedicated for coprocessor use, that can be used as normal RAM when not required by the coprocessor.

• ROM: 224kbytes (for Embedded Software)

32 kbytes (for IC Dedicated Test Software)

- RAM: 6kbytes + 2 kbytes of coprocessor RAM (CRAM)

- EEPROM: 36kbytes

- o on-chip charge pump and independent oscillator

- special write instruction, and interrupt generation on writing

- page write/erase (64 bytes)

- individual page protection bits

(Note1: The protection area is limited to the first 256 bytes of each page. Note2: Use of the protection function is optional and should be selected in [OPT].)

**RNG:** this can generate 16-bit random numbers. Using the RNG enables a unique value to be generated inside the chip, which improves the system security.

**MMC** (Modular Multiplication Coprocessor): this unit consists of the control unit. The control unit is intended to form the basis for efficient implementations of asymmetric cryptography by providing high speed modular multiplication in hardware with a programmable data length from 160 - 2624 bits. As no cryptographic software or algorithm is provided by Renesas for the TOE, the functionality of this coprocessor is included in the evaluated hardware configuration, but its specific use in cryptographic software is not included.

**DES coprocessor:** this hardware engine can be used to provide either DES or triple-DES functions. Countermeasures against information leakage have been integrated into the coprocessor unit to make it highly resistant to such attacks with minimal software overheads or execution time penalties. These countermeasures are always active and make no additional requirements on Security IC Embedded Software. Only triple-DES is claimed as security functionality for this product. For some application contexts, Single-DES may be sufficient <sup>1</sup> - this is a matter for the Security IC Embedded Software security target.

**CRC coprocessor:** CRC (Cyclic Redundancy Check) coprocessor generates codes for detecting errors in data blocks. The CRC codes are created using a generator polynomial CRC-CCITT( $X^{16}+X^{12}+X^5+X^0$ ).

**Interval timer:** the TOE has interval timer 1, interval timer 2, and interval timer 3. These timers are identical and issue an interrupt at intervals which user determined.

**WDT:** the watchdog timer is a powerful tool to help the user software detect and respond to unauthorised program execution. Use of the WDT is optional and should be selected in [OPT].

<sup>&</sup>lt;sup>1</sup> Although strength of cryptographic functions is beyond the scope of a Common Criteria evaluation, triple DES would probably be required to be resistant to attacks performed by an attacker possessing High attack potential. Therefore only triple-DES is claimed as a security function.

**I/O:** I/O comprises I/O-1/IRQ and I/O-2/IRQ (see Figure 1-2). As well as the ISO 7816 standard I/O pin, a further I/O pin is provided for additional use. These pins, together with the power and clock pins, form the electrical interface of the TOE.

**UART:** half-duplex asynchronous mode that conforms to the ISO/IEC standard 7816-3. Full-duplex asynchronous mode that conforms to the ISO/IEC CD standard 10536-4:

**System control logic:** System control logic generates a signal to control the interface between the CPU subsystem and each other subsystem.

**Security logic:** the IC incorporates specialised security logic to help to ensure the correct operation of the TOE, including:

- High and low voltage detection

- High and low frequency detection

- High and low temperature detection

- Illegal instruction detection

- Illegal access detection

- RNG failure detection

The IC also provides protection features to resist leakage attacks – these include bus encryption (which is always active), memory data encryption, and the ability of Security IC Embedded Software to select timing disturbance.

Physical security of the IC is enhanced by the presence of passive and active shielding over critical areas, and by the use of design techniques that obscure the function and operation of the physical layout.

Full details of the operation of the chip and guidance for its use are given in [HM], [OPT], and [UGM].

#### 1.4.1.2 Software

The TOE includes the following software:

#### **IC Dedicated Test Software:**

The IC Dedicated Test Software is integrated into the TOE hardware. It is used for mode transition and testing during IC production, and is not available to users.

#### The RNG On-line Test Software:

The RNG On-line Test Software is provided to perform the on-line test for randomness, as required in [AIS31]. To enable users to deploy the software as necessary, this software is supplied as a listing in [UGM]. Note that the use of this software is part of the intended method of use of the TOE under certain conditions, and it is therefore part of the evaluated configuration.

#### **DES Library for RS-4:**

In order to make compliance with the device's security countermeasure requirements as straightforward as possible for the user, DES Library for RS-4 is provided. The user's manual of the DES library for RS-4 has been described to [UGM].

The DES library has the following function.

- Secure implementation of the DES I/O data encryption key loading.

- Secure implementation of the DES keys loading process.

- Secure implementation of the DES and 3DES algorithm in single block, using the hardware DES coprocessor

All other Security IC Embedded Software (e.g. an operating system) is outside the scope of the TOE. The Security IC Embedded Software is supplied to Renesas by the customer in a secure manner, and is then protected by Renesas' secure production environment.

#### 1.4.1.3 Documents

The TOE Hardware Manual [HM] is supplied as the basic reference for users who are developing Security IC Embedded Software. Guidance for the secure use of RS45C in applications is given in the User Guidance Manual [UGM]. Options and contents of the identification data stored in the EEPROM are described in [OPT].

#### **1.4.2 TOE Intended Usage**

The TOE is intended for use in a range of high security applications, including high speed secure authentication, data encryption or electronic signature. Examples include: PKI, WAP, m-commerce, digital signature, USIM/UMTS, and banking card.

#### **1.4.3 TOE Lifecycle**

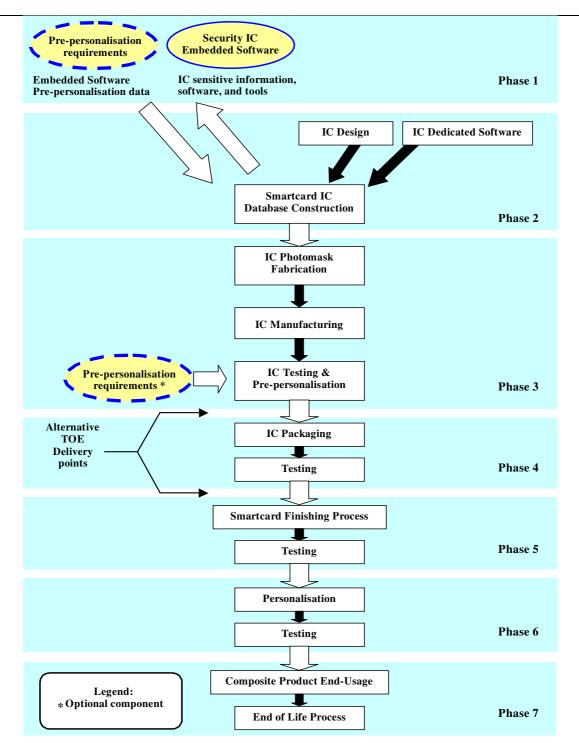

The design and manufacturing lifecycle for the TOE is shown in Figure 1-3 (and in section 7.1.1 of [BSI-PP-0035]). The TOE can be delivered either at the end of phase 3, or at the end of phase 4, as shown in the figure.

Figure 1-3: Design and Manufacturing Lifecycle

The stages shown are as listed below. This Security Target addresses phases 2 and 3 in Figure 1-3. When the TOE is delivered by Renesas as modules rather than in wafer form, phase 4 is also covered under this Security Target.

• Phase 1: Security IC Embedded Software Development – this phase is outside the scope of the TOE, but the results of the software development are inputs to the manufacture of a customer-specific instance of the TOE. Renesas deliver information about the TOE (such as [HM]) to the embedded software developer to enable the Security IC Embedded Software to be written. Development tools (such as emulators) and IC samples are also available to developers. Information and tools are released only under Non-Disclosure Agreement to

ensure their distribution is controlled and limited (this ensures, for example, secure disposal of scrap).

The embedded software for incorporation in the ROM mask is sent via a secure delivery method from the software developer to Renesas, and its secure handling is then ensured by Renesas. Similarly, pre-personalisation data is sent via a secure route to Renesas for injection during the manufacturing stage. Injection of data is described further in section 1.4.4.2. Secure receipt and handling of this data by Renesas is included within the scope of this security target.

• Phase 2: IC Development – this includes system design through logic, circuit and layout design. The Dedicated Test Software is also developed in this phase, to enable testing of the IC at various phases of its manufacture. The Security IC Embedded Software is received from phase 1.

The security of the development environments for the IC and its dedicated software, along with the secure handling of masks are primary concerns of this security target.

• Phase 3: IC Manufacuturing – The masks used to manufacture the various IC layers are created from the layout design during phase 2; ROM masks for the Security IC Embedded Software in a particular instance of the TOE are fabricated after receipt of the software in phase 2. Also, in this phase, wafers containing TOE dies with Security IC Embedded Software are produced. At the end of this process each die is tested and has its prepersonalisation data injected into EEPROM (see section 1.4.4.2).

The secure fabrication and handling of masks, and the security of manufacture, including handling of masks, test software, and pre-personalisation data are primary concerns of this security target.

The TOE may be delivered at this stage as wafers (in which case each die will be set to User Mode). Alternatively, the TOE may be packaged by Renesas and delivered in COT form at the end of phase 4. If the TOE is to be delivered in COT form then at the end of phase 3 it is set to a constrained Test Mode, instead of User Mode, to allow testing of the IC after module manufacturing in phase 4.

This security target covers TOE Delivery at either point, but where wafers are delivered at the end of phase 3, secure handling in phase 4 is a customer responsibility. Note that in all cases the TOE will be set to User Mode before TOE Delivery.

- Phase 4: IC Packaging each wafer is cut into individual dies and its protective packaging applied, along with its contacts. The resulting module is then tested in Test Mode to ensure correct operation, after which it is set to User Mode.

- Phases 5-7: Composite Product Integration, Personalisation and Operational-usage these stages, and their security features, are determined by the customer, and are outside the scope of this security target.

#### **1.4.3.1** Test and User Modes

During manufacturing and production (phases 2-4), the chip makes a series of mode transitions which affect the interface presented. These modes are as follows:

- Test mode makes the IC Dedicated Test Software available, which is used to ensure that only correctly working ICs are delivered.

- User mode makes the IC Dedicated Test Software unavailable and the TOE now provides only the functionality described in [HM]. The software interface presented will be determined by the Security IC Embedded Software.

As explained under the individual lifecycle phases above, the chip is always in test mode in phases 2 and 3. If TOE Delivery takes place at the end of phase 4, then the chip will be in the constrained test mode during phase 4, making a limited set of test functions available to test the correct operation of modules after packaging. However, the TOE is always in User Mode at the point of TOE Delivery, and the transition from User Mode to Test Mode is designed to be very difficult.

### **1.4.3.2 TOE Delivery**

As noted above, the TOE is delivered at the end of either phase 3 or phase 4, as requested by the customer. In either case, the chip will be delivered in User Mode, and Renesas will apply secure delivery procedures for the transport of the TOE from Renesas premises.

### **1.4.4 TOE Environments**

#### **1.4.4.1** Development Environment

Renesas' development environment for the TOE has implemented security measures specifically to ensure the security of the TOE and of Security IC Embedded Software and injection data used in manufacturing ICs for customers. As indicated in section 1.4.3, there are three areas of the development environment:

- Design sites

- Mask manufacture site

- Manufacturing sites

These provide the following main security properties:

- Design sites

- Confidentiality and integrity of logical and physical design

- Testing of TOE security functionality

- Confidentiality and integrity of IC Dedicated Test Software

- Confidentiality and integrity of customer ROM code and injection data (i.e. the Security IC Embedded Software for an instance of the TOE)

- Mask manufacture site

- Confidentiality and integrity of customer ROM code and mask

- Confidentiality and integrity of design and base masks

- Manufacturing sites

- Confidentiality and integrity of base masks

- Confidentiality and integrity of customer ROM mask

- Confidentiality and integrity of test software

- Confidentiality and integrity of injection data

- Production of authentic TOE ICs, correctly implementing the design and including the customer Security IC Embedded Software in ROM.

Security issues for each of these areas are addressed by processes and procedures put in place by Renesas and within the scope of evaluation. The security measures include IT security to protect information stored on Renesas computer systems, as well as physical security measures for secure storage to ensure that design and manufacturing information and objects are only accessible to authorised staff with a need to know the information. Renesas' integrated security concept (ISC) covers the entire development process, from specification, through design and implementation to manufacturing and shipping. ISC is implemented through the use of standards and procedures that form part of the quality system at the heart of Renesas' business. The rigorous adoption and adherence to procedures, including those relating to security, is an integral part of the quality system at the heart of Renesas' business.

The security of the IC Dedicated Test Software at design and manufacturing sites is ensured by the same level of security measures as for the hardware design. This ensures that only authorised persons have access to the software and its related information.

Security IC Embedded Software is received from customers via a secure delivery procedure. Once received by Renesas, this software is also handled with the same level of security as for Security IC design information. As a further measure, the group handling customer software is separate from the IC design team.

### 1.4.4.2 Injection of Manufacturing Identification and Secret Data

In general, although there will be a substantial amount of operating system and application software held in ROM, an IC will also require software to be added after it leaves the manufacturing environment. Operating system software may require additional parts or patches to be loaded, and increasingly applications are expected to be loaded and deleted after Composite Product embedded with Security IC has been issued to users. In order to enable such addition (and deletion) of software to be done securely, there is a generic requirement for identification data and secret data, determined by the IC purchaser, to be injected during manufacture.

The TOE supports this requirement by injecting identification data during the manufacturing process; this data uniquely identifies each IC. In addition, customers may choose to inject further data. The details of the data content and its location in memory are shown in [OPT].

# 2. Conformance Claims

# 2.1 CC Conformance Claim

This ST is compliant with [CC/1], [CC/2] and [CC/3].

Because the ST conforms to [BSI-PP-0035], it includes extended functionality classes defined in section 5 of [BSI-PP-0035]. The ST is therefore [BSI-PP-0035] conformant, [CC/2] extended and [CC/3] conformant. In addition, this ST includes some additional assumptions, threats, objectives and SFRs defined in [PA]. Therefore, this ST is also [PA] conformant.

The Assurance level is EAL5 augmented (for augmentations see section 6.2).

## 2.2 PP Claims

#### 2.2.1 **PP Reference**

This ST conforms to [BSI-PP-0035].

Note that [PA] is used to define additional requirements relating to cryptographic functions. This ST is also [PA] conformant.

#### 2.2.2 **PP** Tailoring

FCS\_RNG.1 is completed with a quality metric – see section 6.1.1.5.

FAU\_SAS.1 is completed with a quality metric – see section 6.1.1.2.

#### 2.2.3 **PP Additions**

The inclusions from [BSI-PP-0035] are clearly shown in the relevant section titles. All other threats, assumptions, objectives, extended components, and SFRs, in sections 3.2.2, 3.3.2, 3.4.2, 3.4.3, 4.1.2, 4.1.3, 4.2.3, and 6.1.2 are additional to those in the PP.

## 2.3 Package Claim

The assurance level for this Security Target is EAL5 augmented. The augmentations to EAL5 are ALC\_DVS.2, and AVA\_VAN.5.

### 2.4 Conformance Rationale

#### 2.4.1 CC Conformance Rationale

This ST implements all of the requirements of [CC/1], [CC/2] and [CC/3] by inclusion (as shown in each of the relevant sections), and hence no further rationale is required.

### 2.4.2 PP Claim Rationale

This ST for the TOE type as described in section 1.3 implements all of the requirements, security problem definition, objectives and security requirements, of [BSI-PP-0035] by inclusion (as shown in each of the relevant sections), and hence no further rationale is required.

#### 2.4.3 Package Claims Rationale

This ST implements all of the requirements of EAL5 augmented.

[BSI-PP-0035] requires the assurance level EAL4 augmented. Regarding the Application Note 21 of [BSI-PP-0035] the changes which are needed for EAL5 are described in the different relevant sections of this Security Target.

# 3. Security Problem Definition

## **3.1 Description of Assets**

This section defines the assets to be protected by the TOE. Section 3.1 of [BSI-PP-0035] gives the assets relating to the threats, and these are summarised below.

The assets to be protected are:

• the User Data

this includes injection/pre-personalisation data and data generated and managed by the Security IC Embedded Software (subject to adequate protection by the software, see A.Key-Function, A.Plat-Appl and A.Resp-Appl in section 3.4)

- the Security IC Embedded Software stored and in operation, comprising

- Hard-coded Embedded Software this is fixed and generally consists of parts or all of the operating system, and parts or all of a number of applications

- Soft-coded Embedded Software this may include parts of the operating system or applications.

Both of these types of asset need to have their confidentiality and integrity protected.

A further asset is:

• the security services provided by the TOE for the Security IC Embedded Software

In particular integrity of the Security IC Embedded Software means that the Security IC Embedded Software will be correctly executed, which includes the correct operation of the TOE's functions.

Because random numbers are likely to be used by embedded software for generating cryptographic keys, another asset is:

• the random numbers generated by the  $TOE^2$

To be able to protect these assets the TOE shall protect its security functionality. Therefore critical information about the TOE shall be protected. Critical information includes:

• logical design data, physical design data, IC Dedicated Software, and configuration data

In addition, the following will also contain information about the TOE.

• Initialisation Data and Pre-personalisation Data, specific development aids, test and characterisation related data, material for software development support, and photomasks.

$<sup>^{2}</sup>$  The confidentiality of random numbers is generally protected by embedded software (which is responsible for requesting random numbers). However, it is important that random numbers should not be subject to leakage (cf. T.Leak-Inherent), because of their potential role in cryptographic key generation.

Such information and the ability to perform manipulations assist in threatening the primary assets.

### 3.2 Threats

#### **3.2.1** Threats Defined in [BSI-PP-0035]

This section adopts the threats to ICs defined in section 3.2 of [BSI-PP-0035].

The TOE has the following high-level security concerns, as in section 3.1 of [BSI-PP-0035]:

- SC1 integrity of User Data and of the Security IC Embedded Software (while being executed/processed and while being stored in the TOE's memories).

- SC2 disclosure of User Data and of the Security IC Embedded Software (while being processed and while being stored in the TOE's memories).

- SC3 correct operation of the security services provided by the TOE for the Security IC Embedded Software.

- SC4 deficiency of random numbers.

The above high-level security concerns are refined below by defining specific threats. Note that manipulation of the TOE is only a means to threaten User Data or the Security IC Embedded Software and is not a success for the attacker in itself.

These security concerns are derived from considering the operational usage by the end-consumer (phase 7) since

- Phase 1 and the Phases from TOE Delivery up to the end of Phase 6 are covered by assumptions, and

- The development and production environment starting with Phase 2 up to TOE Delivery are covered by an organisational security policy

#### **3.2.1.1** Standard Threats

See section 3.2 of [BSI-PP-0035], and the example attack scenarios in section 7.3 of [BSI-PP-0035]. For completeness, the threats are summarised below.

T.Leak-Inherent Inherent Information Leakage

An attacker may exploit information which is leaked from the TOE during usage of the Security IC in order to disclose confidential User Data as part of the assets.

No direct contact with the Security IC internals is required here. Leakage may occur through emanations, variations in power consumption, I/O characteristics, clock frequency, or by changes in processing time requirements.

#### **T.Phys-Probing**

**Physical Probing**

An attacker may perform physical probing of the TOE in order:

- (i) to disclose User Data

- (ii) to disclose/reconstruct the Security IC Embedded Software

- (iii) to disclose other critical information about the operation of the TOE to enable attacks disclosing or manipulating the User Data or the Security IC Embedded Software.

Physical probing requires direct interaction with the Security IC internals. Techniques commonly employed in IC failure analysis and IC reverse engineering efforts may be used. Before that, hardware security mechanisms and layout characteristics need to be identified. Determination of software design, including treatment of User Data may also be a pre-requisite.

**T.Malfunction** Malfunction due to Environmental Stress

An attacker may cause a malfunction of the TSF or of the Security IC Embedded Software by applying environmental stress in order to

- (i) modify security services of the TOE

- (ii) modify functions of the Security IC Embedded Software.

- (iii) deactivate or affect security mechanisms of the TOE to enable attacks disclosing or manipulating the User Data or the Security IC Embedded Software

This may be achieved by operating the Security IC outside its normal operating conditions.

The modification of security services of the TOE may e.g. affect the quality of random numbers provided by the random number generator up to undetected deactivation when the random number generator does not produce random numbers and the Security IC Embedded Software gets constant values. In another case errors are introduced in executing the Security IC Embedded Software. To exploit this an attacker needs information about the functional operation, e.g. to introduce a temporary failure within a register used by the Security IC Embedded Software with light or a power glitch.

#### T.Phys-Manipulation Physical Manipulation

An attacker may physically modify the Security IC in order to

- (i) modify User Data,

- (ii) modify the Security IC Embedded Software

- (iii) modify or deactivate security services of the TOE, or

- (iv) modify security mechanisms of the TOE to enable attacks disclosing or manipulating the User Data or the Security IC Embedded Software.

The modification may be achieved through techniques commonly employed in IC failure analysis and IC reverse-engineering. The modification may result in the deactivation of a

security feature. Determination of software design including treatment of User Data may be a pre-requisite. Changes to circuitry or data can be permanent or temporary.

In contrast to malfunctions (refer to T.Malfunction), the attacker requires to gather significant knowledge about the TOE's internal construction here.

T.Leak-Forced Forced Information Leakage

An attacker may exploit information which is leaked from the TOE during usage of the Security IC in order to disclose confidential User Data as part of the assets even if the information leakage is not inherent but caused by the attacker.

This threat pertains to attacks where methods described in "Malfunction due to Environmental Stress" (refer to T.Malfunction) and/or "Physical Manipulation" (refer to T.Phys-Manipulation) are used to cause leakage from signals which normally do not contain significant information about secrets.

Differential Fault Analysis (DFA) is an example of an attack based on the forced leakage threat.

**T.Abuse-Func**Abuse of Functionality

An attacker may use functions of the TOE which may not be used after TOE Delivery in order to

- (i) disclose or manipulate User Data

- (ii) manipulate (explore, bypass, deactivate or change) security services of the TOE or of the Security IC Embedded Software or

- (iii) manipulate (explore, bypass, deactivate or change) functions of the Security IC Embedded Software or

- (iv) enable an attack disclosing or manipulating the User Data or the Security IC Embedded Software.

For the TOE, T.Abuse-Func concerns the threat of unauthorised access to the IC Dedicated Test Software, which is rendered inaccessible by placing the IC into User Mode before TOE Delivery (see section 1.4.3).

#### **3.2.1.2** Threats Related to Security Services

T.RND Deficiency of Random Numbers

An attacker may predict or obtain information about random numbers generated by the TOE security service for instance because of a lack of entropy of the random numbers provided.

An attacker may gather information about the random numbers produced by the TOE security service. Because unpredictability is the main property of random numbers this may be a problem in case they are used to generate cryptographic keys. Here the attacker is expected to take advantage of statistical properties of the random numbers generated by the TOE.

Malfunctions or premature ageing are also considered which may assist in getting information about random numbers.

Attacks on random number generation are significant because the random numbers generated may be used as secrets - e.g. to generate cryptographic keys.

Under the threat T.RND, the attacker is assumed to take advantage of statistical properties of the random numbers generated by the TOE without specific knowledge about the RNG itself.

#### **3.2.2** Other Threats

The TOE makes available facilities that are useful for embedded software to use in addressing the threats that it may face. This introduces an additional high-level security concern for the TOE:

- SC5 attacks on the Security IC Embedded Software may be made, and the software may not be able to respond to the attacks.

- **T.NoSWResponse** Inability of Security IC Embedded Software to respond to an attack

An attacker may abuse the weak point of the TOE that does not allow the Security IC Embedded software to enter secure state, in order to disclose the User Data.

This threat does not address the particular details of individual attacks, but recognises that Security IC Embedded Software may make checks on its own state to enhance protection against a variety of attacks (including those aimed at inducing errors by software or external means). For such checks to be useful, there must also be ways for the software to respond to the attack (e.g. by preventing further processing).

## **3.3** Organisational Security Policies

### 3.3.1 Policy Requirement from [BSI-PP-0035]

The following policy requirement is taken from section 3.3 of [BSI-PP-0035].

**P.Process-TOE** Protection during TOE Development and Production

An accurate identification must be established for the TOE. This requires that each instantiation of the TOE carries this unique identification.

Assets relating specifically to P.Process-TOE are given in section 3.1 of [BSI-PP-0035].

Renesas implement the security measures to satisfy this policy requirement, and these are assessed as part of evaluation and certification against this ST. However, since they are not directly relevant to users of the TOE, the detailed measures and processes that implement the policy are not given here.

Note that the inclusion of identification information in EEPROM is described in more detail in section 1.4.4.2. This part of the policy establishes a basis for evaluation and security of software running on the chip, by ensuring that a TOE can be identified. Note that procedural measures

(including Renesas' secure delivery procedures) will generally be required to ensure that TOE ICs are genuine, unless the Security IC Embedded Software contains functionality to authenticate the  $IC^3$ .

P.Process-TOE covers identification of hard-coded Embedded Software (via identification of the ROM mask); soft-coded Embedded Software will generally need to provide its own identification.

### **3.3.2 Policy Requirement from [PA]**

As an additional policy, the TOE provides specific security functionality which can be used by the Security IC Embedded Software for cryptographic algorithm implementation. The policy P.Add-Functions is therefore adopted from [PA]. In the following policy, specific security functionality is listed which is not derived from threats identified for the TOE's environment because it can only be decided in the context of the Composite Product application, against which threats the Security IC Embedded Software will use the specific security functionality.

**P.Add-Functions** Additional Specific Security Functionality

The TOE shall provide the following specific security functionality to the Security IC Embedded Software:

• Triple Data Encryption Standard (3DES)

## 3.4 Assumptions

#### 3.4.1 Assumptions from [BSI-PP-0035]

Appropriate "Protection during Packaging, Finishing and Personalisation (A.Process-Sec-IC)" must be ensured after TOE Delivery up to the end of Phase 6, as well as during the delivery to Phase 7 as specified below.

A.Process-Sec-IC Protection during Packaging, Finishing and Personalisation

It is assumed that security procedures are used after delivery of the TOE by the TOE Manufacturer up to delivery to the end-consumer to maintain confidentiality and integrity of the TOE and of its manufacturing and test data (to prevent any possible copy, modification, retention, theft or unauthorised use).

This means that the Phases after TOE Delivery are assumed to be protected appropriately.

The information and material produced and/or processed by the Security IC Embedded Software Developer in Phase 1 and by the Composite Product Manufacturer can be grouped as follows:

- the Security IC Embedded Software including specifications, implementation and related documentation,

<sup>&</sup>lt;sup>3</sup> For example, a hash or digital signature over a known area of memory might be provided by software.

- pre-personalisation and personalisation data including specifications of formats and memory areas, test related data,

- the User Data and related documentation, and

- material for software development support

as long as they are not under the control of the TOE Manufacturer.

The developer of the Security IC Embedded Software must ensure the appropriate "Usage of Hardware Platform (A.Plat-Appl)" while developing this software in Phase 1 as specified below.

#### A.Plat-Appl Usage of Hardware Platform

The Security IC Embedded Software is designed so that the requirements from the following documents are met:

- (i) TOE guidance documents (refer to the Common Criteria assurance class AGD) such as the hardware data sheet, and the hardware application notes:

i.e. TOE hardware manual [HM], user guidance manual [UGM], and the hardware application notes

- (ii) findings of the TOE evaluation reports relevant for the Security IC Embedded Software as documented in the certification report.

The developer of the Security IC Embedded Software must ensure the appropriate "Treatment of User Data (A.Resp-Appl)" while developing this software in Phase 1 as specified below

A.Resp-Appl Treatment of User Data

All User Data is owned by Security IC Embedded Software. Therefore, it must be assumed that security relevant User Data (especially cryptographic keys) are treated by the Security IC Embedded Software as defined for the specific application context.

This assumption requires that the Security IC Embedded Software define and positively manage its security relevant User Data, in the manner required by the application context. Without this, the protection provided by the TOE itself may be of no use if the Security IC Embedded Software itself allows data to be compromised.

Examples of embedded software security concerns are given in section 7.2 of [BSI-PP-0035].

#### 3.4.2 Assumptions from [PA]

**A.Key-Function** Usage of Key-dependent Functions

Key-dependent functions (if any) shall be implemented in the Security IC Embedded Software in a way that they are not susceptible to leakage attacks (as described under T.Leak-Inherent and T.Leak-Forced).

Note that here the routines which may compromise keys when being executed are part of the Security IC Embedded Software. In contrast to this the threats T.Leak-Inherent and T.Leak-Forced address (i) the cryptographic routines which are part of the TOE and (ii) the processing of User Data including cryptographic keys.

An example of the type of attack relevant to this assumption would be analysis of the power consumption of the IC during the cryptographic operation.

Note here that the functions considered in this assumption are part of the Security IC Embedded Software; T.Leak-Inherent and T.Leak-Forced address the cryptographic functions that are part of the hardware.